Se basa en el nuevo estándar que promete cambiar la industria de los semiconductores, las compañías más importantes del rubro de los semiconductores se han aliado para crear un consorcio que se propone estandarizar el ecosistema de chiplets. Estamos hablando de Intel, ARM, Qualcomm, TSMC y Samsung, entre otras; las mismas unirán esfuerzos en busca de reducir los costos de producción y universalizar la interconexión de chiplets. Para ello proponen el Universal Chiplet Interconnect Express (UCIe), como la respuesta para el diseño y la fabricación de los SoCs del futuro.

El proyecto es tan interesante como técnico; por eso trataremos de explicar sus puntos principales de la manera más comprensible posible. Es importante tener en cuenta que detrás de esta iniciativa no solo se encuentran los diseñadores de chips más importantes del mundo, sino también corporaciones como Microsoft, Meta (Facebook) y Google, como proveedoras de servicios en la nube.

A través de UCIe, sus promotores buscan estandarizar la interconexión entre chiplets basándose en unos diseños open source. Esto busca «romper» los parámetros que existen en la actualidad, donde las soluciones son propietarias y eso impide la compatibilidad directa entre los chiplets diseñados por distintas compañías.

-¿Qué son los chiplets, al fin y al cabo?

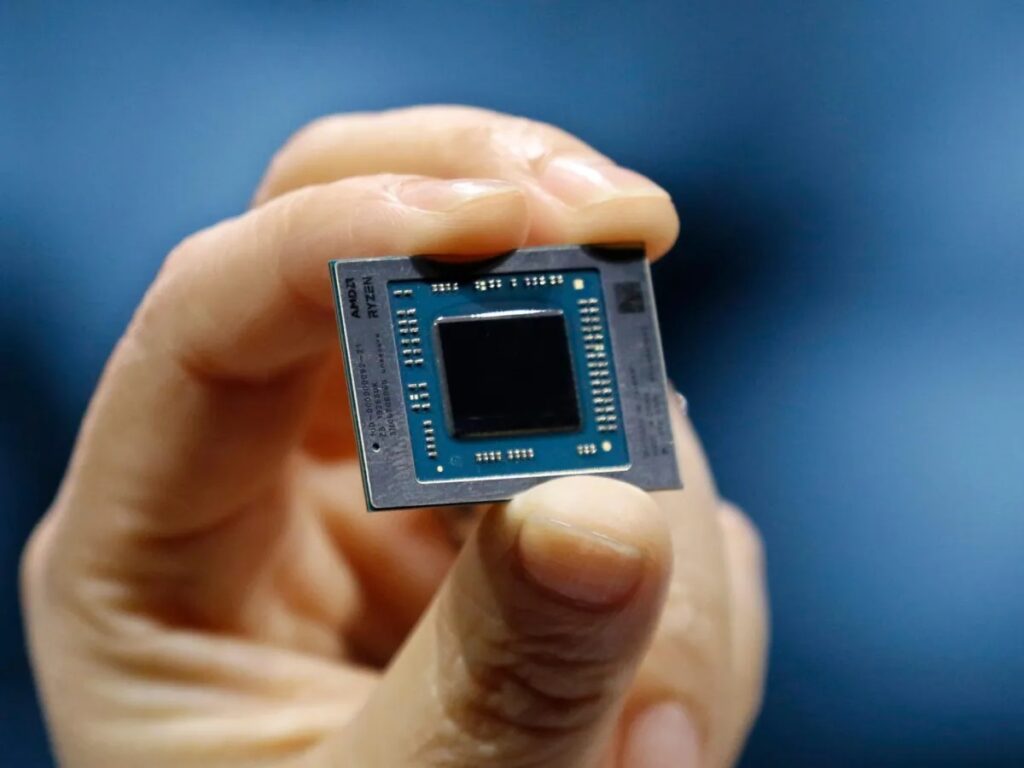

El término «chiplet» no es necesariamente nuevo, aunque recién en el último lustro se ha escuchado con mayor asiduidad. Los chiplets son la alternativa a la arquitectura monolítica para el diseño y la fabricación de procesadores. Estamos hablando de la utilización de componentes independientes que se agrupan para conformar un chip más grande.

Esto trae consigo varios beneficios. En primera instancia, al lidiar con chips más pequeños es posible abaratar los costos de producción; a su vez, al tratarse de un armado modular, si ocurre un problema con una de las partes, es posible repararlo. Así, si se registra un fallo en la memoria pero no en los núcleos, no se debe descartar el procesador por completo (como sí ocurre en el diseño monolítico) sino solo el chiplet que está presentando inconvenientes.

No obstante, los chiplets no están exentos de algunos puntos en contra. Históricamente, su aspecto más problemático es la latencia, que se produce porque los distintos circuitos no están en contacto directo. Esto significa que los datos demoran más tiempo en viajar entre los chiplets. Vale destacar, de todos modos, que UCIe promete atender esta flaqueza.

AMD e Intel son las compañías que más han empujado la adopción de los chiplets en el diseño de su respectivo hardware, en los últimos años. Una apuesta que comenzó a fines de 2018 con la introducción de la arquitectura AMD Zen 2 de 7 nanómetros y los problemáticos procesadores Intel Sunny Cove de 10 nm.

-El estándar UCIe se propone cambiar los SoCs del futuro

Una de las analogías que más se ha visto en estos días para explicar cómo funcionará esta propuesta es la de los bloques de LEGO. Es que el consorcio detrás de Universal Chiplet Interconnect Express propone que el nuevo estándar permita que los fabricantes de SoCs elijan qué componentes utilizar, sin importar quién los fabrique. Para ello, la especificación 1.0 de UCIe aprovecha dos protocolos que muy arraigados en la industria, como son CXL y PCIe. Además, promete un rendimiento rentable y ser eficiente en el consumo de energía.

Si buscamos una comparación súper simplificada de lo que le aportará este nuevo estándar a la industria de los semiconductores, podríamos decir que bajo UCIe los fabricantes podrán incorporar distintos chiplets a sus diseños con la misma facilidad que hoy podemos instalar una unidad de estado sólido vía NVMe, o una tarjeta gráfica a través de PCIe.

Si buscan información más técnica sobre cómo se pretende implementar la estandarización para el ecosistema de chiplets, Tom’s Hardware ha publicado un muy interesante artículo. Allí se explora cuáles son los objetivos de rendimiento, así como la implementación de las capas físicas y de protocolo, entre otras cuestiones.

Los principales exponentes de la industria de los semiconductores (tanto diseñadores como fundiciones) estén a bordo de Universal Chiplet Interconnect Express, es muy prometedor. De todos modos, aún se debe transitar un largo camino para ver plasmados los resultados de esta iniciativa.

Y mientras este consorcio da sus primeros pasos, la expectativa está puesta en que más empresas se sumen. Los promotores de UCIe ya se proponen trabajar en definir varios puntos importantes para el futuro del estándar; entre tantos, el factor de forma de los chiplets, la gestión de los mismos, la optimización de la seguridad, y otros «protocolos esenciales».

«El hecho de que sea un estándar abierto con un modelo plug-and-play, inspirado en varios estándares exitosos, y lanzado por el grupo adecuado de líderes de la industria garantizará su adopción generalizada. Prevemos que la próxima generación de innovaciones ocurrirá a nivel del chiplet, lo que permitirá que un conjunto de chiplets ofrezca diferentes capacidades para que el cliente elija la que mejor se adapte a los requisitos de su aplicación», aseguraron.